字體:小 中 大

字體:小 中 大 |

|

|

|

| 2022/06/06 13:46:38瀏覽1952|回應0|推薦14 | |

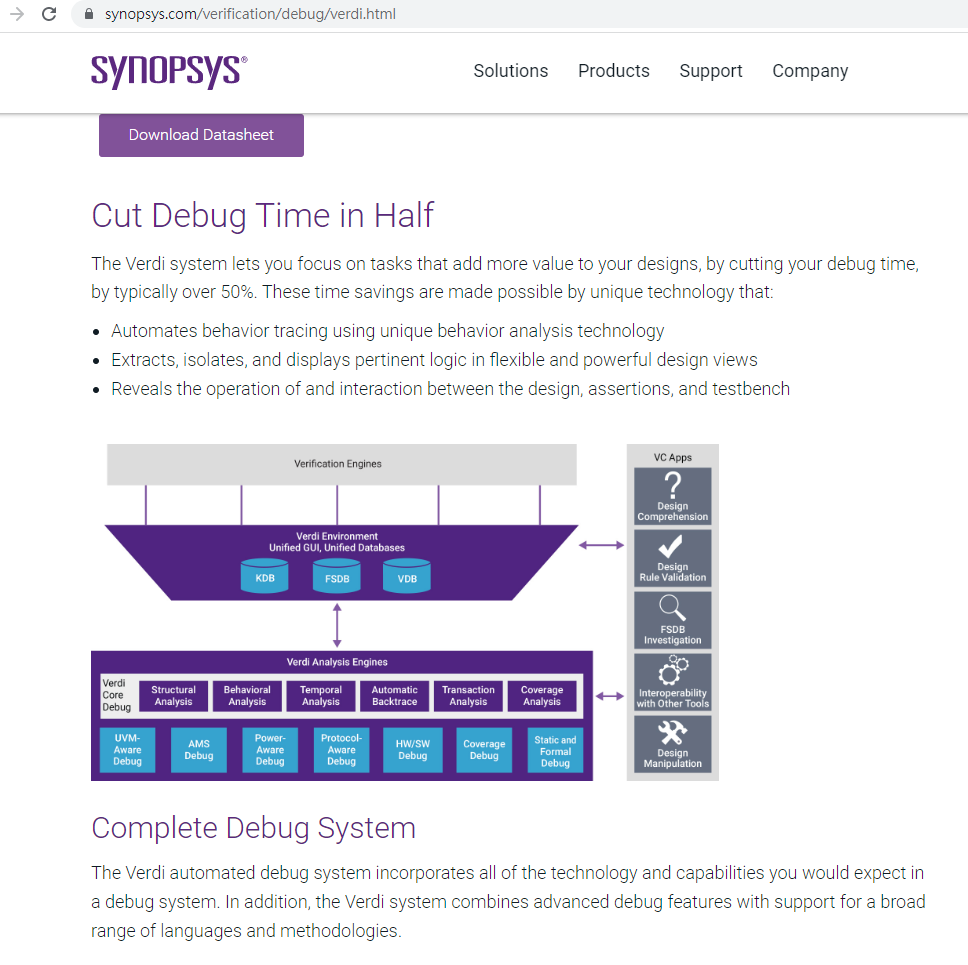

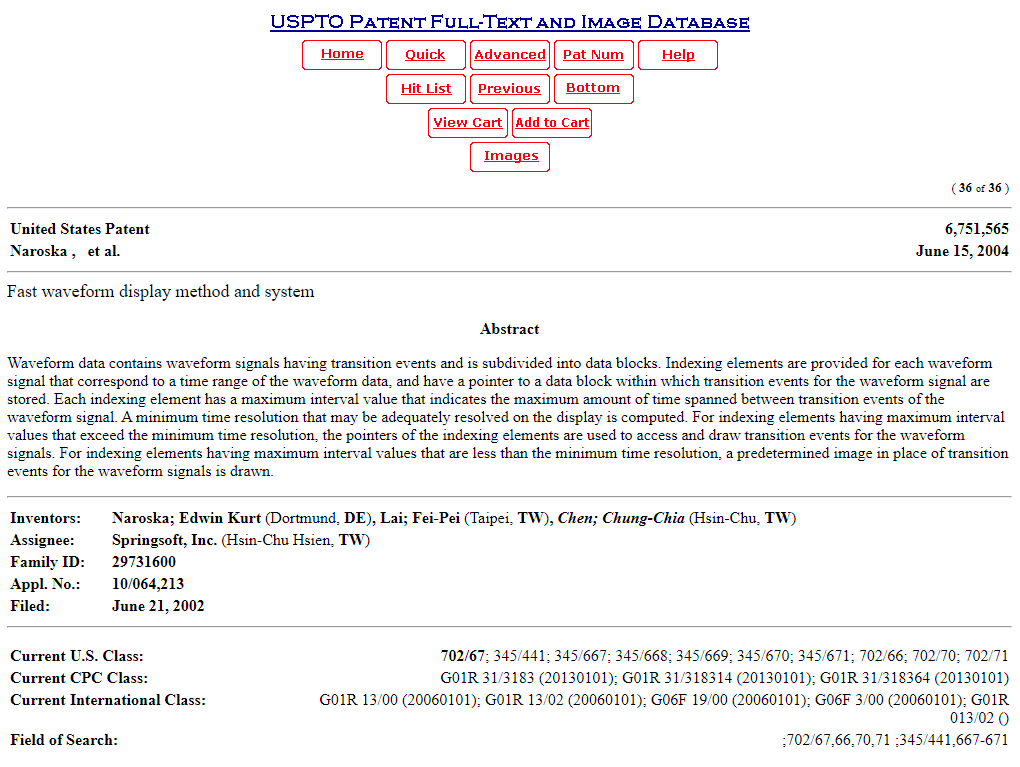

今年的四月下旬 (2022 年 4 月),突然接到一位很久以前的同事打來的電話,剛接通確認之際,他很驚訝這古老的號碼還找得到我,興奮地說道: 順道一提的事情是,在帶領 Bus Protocol Checker 小組的期間,每次的開會,公司的 CEO 都有來參與會議,之後筆者離開了公司,離職超過半年後的當年 11 月,全家正在南部度假時,接到前公司行政人員的電話與 e-mail 來信,原來是 bus protocol checker 要申請美國專利,而筆者是原計畫的帶領者,即使離職了,公司沒有忘記筆者的貢獻,所以寄來專利申請的填寫文件,要將筆者列入其中的一員(筆者在職期間,幫公司申請到兩項美國專利,一個是自己做的 FSDB,另一個是擔任帶領者的 bus protocol checker),筆者相信這是公司的 CEO 特別交代如此這麼做的,因為公司的 CEO 一直對筆者不錯,記得在離職的前夕,CEO 找筆者聊天時,除了試著詢問還有沒有機會留下來之外,也聊到他晚上常常睡不著,因為心裡覺得很煩,筆者也能夠體會,畢竟公司上市後曾經當過眾所矚目的焦點,而且很多人也都在密切觀察公司未來的營運情況,營運績效每年都要成長而且要符合外界預期的壓力,大到令 CEO 操煩到睡不著覺,這其中當然一定還有其它的壓力因素;當時 CEO 講完「晚上常常睡不著、心裡很煩」這句話後,他的眼神凝視著書桌前方,不發一語地靜默了一陣子,筆者雖能約略體會那心情,但也幫不上忙;離開公司若干年後,公司被全球 EDA 龍頭併購,這可說是一個很漂亮的出場,相信 CEO 在漂亮出場之後,已經不會再心煩地睡不著覺。 查了一下 waveform database(FSDB) 與整個 EDA 現況,FSDB 仍是 front end debugging tool 的主要支柱之一,而 EDA 產業的產值已經從 USD 4B 上升到 10B 左右,根據 2000 年時 EDA 產業的產值為 4B 為基準,歷經 21 年成長到 10B,平均年成長率約 4.46%,對早已是個成熟的產業來說,這樣的年成長率還算不錯,儘管有段時期是連續好幾年沒有成長。

Well, 都已經是過去的事情了,沒有要做 waveform database。 Anyway, thanks for the information. 備註一: 備註二:

nWave is not a simulator, it is a waveform viewer. If customers are looking for simulators, then they should turn to VCS, NC-Verilog, or ModelSim. If they want to view an FSDB file, then Verdi is what they need, because nWave is a component of Verdi. An FSDB file is not a flat ASCII file, it is in binary format. You may wonder that some of its contents seem to be ASCII, well, only some pieces of information in the header section are in ASCII format, the rest are all in binary format, such as chain areas, tree blocks (design hierarchy; $scope def., $var def., $upscope def.), and value change blocks. Why do I know these details? Well, I was working as a senior software engineer and associate manager in EDA sector from 1996 through 2004, and I was the one who designed and implemented this proprietary waveform database (as known as Fast Signal DataBase -- FSDB), including the two main components -- FSDB Reader and Writer, and related utilities, such as vfast, fsdb2vcd, and xloc. FSDB Writer (written in C) is the kernel of $fsdbDumpfile(), this verilog task $fsdbDumpfile() queries the value changes via PLI (an interface provided and supported by simulators; PLI is a set of APIs defined by IEEE) and calls FSDB Writer API to build up in-core data structures to store value changes, and FSDB Writer will flush in-core value changes to an fsdb file if the memory usage comes to a specific extent (memory limit), so for a single simulation run, there may be a lot of flush sessions. FSDB Reader (written in C++) is the kernel of nWave, it reads value changes from an FSDB file and builds up in-core data structures (such as Double Linked List, AVL trees, and Heap trees) for value change traverse and displaying, the double linked varied-size value change chunks are for sequential traverse, while adapted AVL trees across value change chunks are for random traverse. The gist of my proprietary waveform database design (FSDB) is "the mapping between logical space and physical space (disk offset)," the rest are all about data encoding/decoding and compression/decompression, adapted data structures and algorithms for front-end simulation and debugging, partial load of value changes, critical section control (locking for interactive debugging and viewing), and performance. My name in Chinese is spelled as "Chen, Chung-Chia", and the US Patent about my work in EDA sector is as follows: US Patent Number 6,751,565 <Fast waveform display method and system> The other two inventors are professors from Germany (Dortmund University) and Taiwan (National Taiwan University), their jobs were sharing academic point of views and ideas.

|

|

| ( 創作|其他 ) |