我們知道想要提高CPU的運算效能,不能夠簡單通過堆砌內核的方式。那麼能不能簡單提高CPU主頻,讓CPU每個內核更快的算出結果呢?為什麼持CPU製程牛耳的Intel,不再勇攀主頻高峰了呢?其實,瓶頸主要在於散熱,我們來詳細了解一下個中原因。

為什麼CPU會發熱

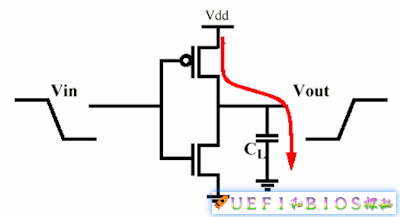

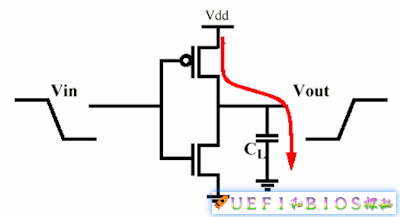

從含有1億4000萬個場效應晶體管FET的奔騰4到高達80多億的Kabylake,Intel忠實的按照摩爾定律增加著晶體管的數目。這麼多個FET隨著每一次的翻轉都在消耗者能量。一個FET的簡單示意圖如下:

當輸入低電平時,CL被充電,我們假設a焦耳的電能被儲存在電容中。而當輸入變成高電平後,這些電能則被釋放,a焦耳的能量被釋放了出來。因為CL很小,這個a也十分的小,幾乎可以忽略不計。但如果我們以1GHz頻率翻轉這個FET,則能量消耗就是a × 10^9,這就不能忽略了,再加上CPU中有幾十億個FET,消耗的能量變得相當可觀。

耗能和頻率的關係

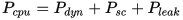

從圖示中,也許你可以直觀的看出,能耗和頻率是正相關的。這個理解很正確,實際上能耗和頻率成線性相關。能耗關係公示是(參考資料2):

P代表能耗。C可以簡單看作一個常數,它由製程等因素決定;V代表電壓;而f就是頻率了。理想情況,提高一倍頻率,則能耗提高一倍。看起來並不十分嚴重,不是嗎?但實際情況卻沒有這麼簡單。

我們這裡要引入門延遲(Gate Delay)的概念。簡單來說,組成CPU的FET充放電需要一定時間,這個時間就是門延遲。只有在充放電完成後採樣才能保證信號的完整性。而這個充放電時間和電壓負相關,即電壓高,則充放電時間就短。也和製程正相關,即製程越小,充放電時間就短。讓我們去除製程的干擾因素,當我們不斷提高頻率f後,過了某個節點,太快的翻轉會造成門延遲跟不上,從而影響數字信號的完整性,從而造成錯誤。這也是為什麼超頻到某個階段會不穩定,隨機出錯的原因。那麼怎麼辦呢?聰明的你也許想到了超頻中常用的辦法:加壓。對了,可以通過提高電壓來減小門延遲,讓系統重新穩定下來。

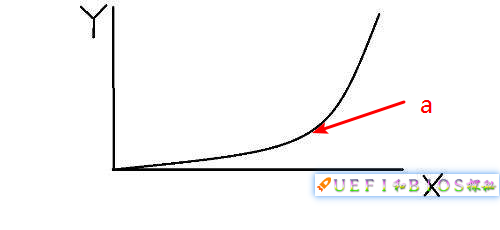

讓我們回頭再來看看公式,你會發現電壓和功耗可不是線性相關,而是平方的關係!再乘以f,情況就更加糟糕了。我們提高頻率,同時不得不提高電壓,造成P的大幅提高!我們回憶一下初中學過的y=x^3的函數圖:

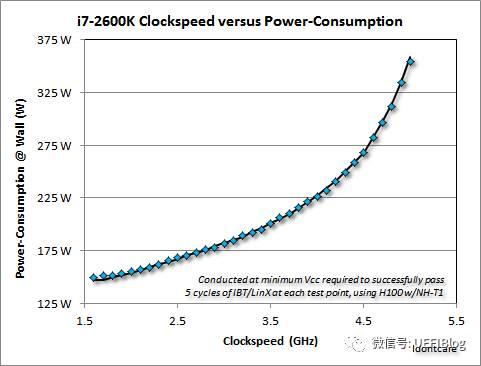

Y在經過前期緩慢的提高後在a點會開始陡峭的上升。這個a就是轉折點,過了它,就劃不來了。功耗和頻率的關係也大抵如此,我們看兩個實際的例子:

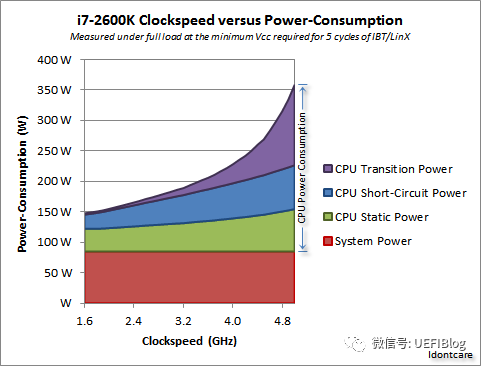

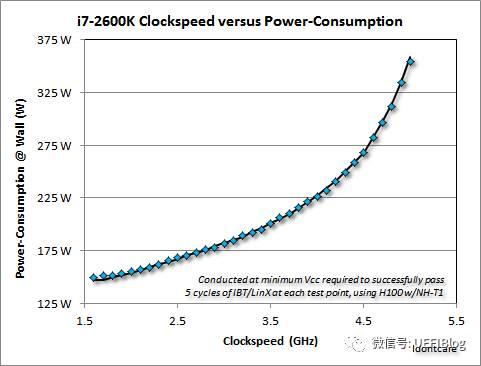

i7-2600K頻率和功耗的關係

i7-2600K頻率和功耗的關係 Exynos頻率和功耗的關係

Exynos頻率和功耗的關係

從ARM和X86陣營來看,他們能耗曲線是不是和冪函數圖很像?

不可忽視的其他因素

現實情況比這個更複雜。實際上,上面公式裡的P只是動態能耗。CPU的整體功耗還包括短路功耗和漏電功耗:

短路功耗是在FET翻轉時,有個極短時間會有電子直接跑掉。它和電壓、頻率正相關。

漏電功耗是電子穿透MOSFET的洩漏情況,它和製程與溫度有關。

綜合這些,我們看一個實際的例子:

這裡的Transition Power就是動態能耗,可以看出它隨著頻率陡峭上升;短路功耗和頻率幾乎呈現線性關係;而Static power就是指漏電功耗,它也上升是因為頻率上升導致溫度上升,從而漏電加重。

我們這裡引入熱密度的概念,即單位面積發出熱的數量。從此圖看出,隨著頻率的提高,各種因素綜合疊加導致功耗上升嚴重,而芯片尺寸不變,從而熱密度提高很快,現有散熱設備短時間內排不出這麼多熱量,就會造成死機等現象。這也是為什麼超頻往往需要很好的散熱設備的原因。

一個腦洞

我們最後開一個腦洞:假設沒有散熱問題,沒有門延遲,一個完美的世界裡,頻率有上限嗎?這是個很有意思的思考。大家都知道電信號在導線裡的傳播速度很快,接近光速。我們這裡就取光速:每秒30萬公里。相信每個略微了解相對論的人都知道光速是物理極限,我們這裡不討論科幻問題。因為沒有門延遲,電信號以光速傳播。光速,這個數字很大,但我們的頻率可是以G為單位,就是10^9,也非常大。在1GHz的情況下,電信號只能傳播30cm!再遠就會有相位差。10GHz的話,才能傳播3cm。晶圓大小是300mm,如果我們做出個和它一樣大的CPU Die,也許最高頻率只有1GHz。而現在CPU的die大小差不多1cm,所以理論上30GHz是極限頻率!

結論

在沒有強勁散熱的情況下超頻會減少CPU壽命,經由液氮製冷的加持,CPU的頻率在極限玩家的幫助下才能挑戰9GHz。這對於我們日常電腦用戶來說十分遙遠。而且在可以預見的未來,CPU頻率因為熱密度的關係並不會大幅提高,我們可能永遠也看不到10GHz的矽基CPU。也許只有在拋棄矽或者轉換到量子計算,CPU頻率才會有翻天覆地的變化。

單純追求高主頻會讓功耗急劇上升,經濟上並不合算,現在CPU廠商早就放棄了單純追求高主頻,轉而提高每瓦性能。實際上目前的CoffeeLake 3.8G的CPU相比奔騰4的3.8G,Benchmark跑下來效能提高了十幾倍,而功耗反倒下降不少!這全拜改進架構的福。在吸取了基於netburst深度流水來提高主頻,卻被“譽為”高頻低能的奔騰4教訓後,這也是Intel等芯片製造商努力的方向。

目前 IT產業面臨PCIe 4.0 / 5.0 正翻轉著整個電子產業,帶動的兩個主軸是 SI/ PI ,為什麼呢? 呵呵 ~ 不能回歸系統工程 看清問題,若是錯用小聰明度日,這一波可能會讓你錯過此生而無處回頭。話說 蔡英文 希望你能理解,勿枉過此生,誤人誤己。

字體:小 中 大

字體:小 中 大

i7-2600K頻率和功耗的關係

i7-2600K頻率和功耗的關係 Exynos頻率和功耗的關係

Exynos頻率和功耗的關係