字體:小 中 大

字體:小 中 大 |

|

|

||

| 2013/07/29 00:21:25瀏覽2354|回應0|推薦0 | ||

Security(SEC) Phase SEC Phase 簡介 SEC是reset 或 power-on 後 PI ( Platform Initialization)的第一個phase定義在Platform Initialization Specification, Ver. 1.2.1,Volume 1, Chapter 13。SEC必須確保firmware的 "完整"。 SEC他是相依於platform及CPU的,也就是說必須針對不同的CPU或平台來做移植。另外,SEC大部分的實作都是在assembly下的,而且是不可以壓縮的。 SEC Phase 的責任 SEC有四個主要的任務分別如下: 1. Restart SEC必須要處理所有的platform restart event,包含開機、重開機或是其他異常的重啟。 2. Memory Sotre SEC必須要建立一塊臨時的memory在系統初始化前使用。使用例如CAR( Cache as Ram)或SRAM的技術。 3. Root of Trustestart SEC從power on 開始要尋找和驗證PEI的最初步驟。目的是要保證Processor最開始的code是可以信賴的。 4. Passing 傳送Handoff訊息和把control給PEI Fondation。傳送的訊息包含了a. 平台狀態、b. BFV(Boot Firmware Volume)位置及大小、c. temporary RAM的位置大小等等。 SEC透過 EFI_PEI_STARTUP_DESCRIPTOR 將上述Passing的資料pass給PEI。 EFI_PEI_STARTUP_DESCRIPTOR 的資料結構是長這樣子的:

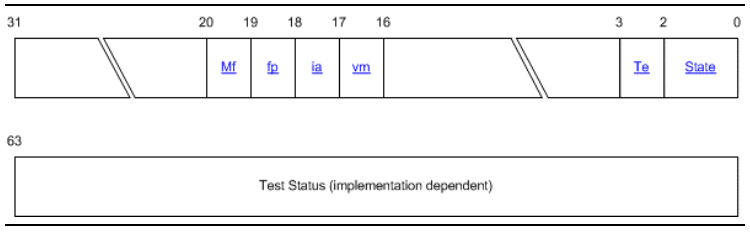

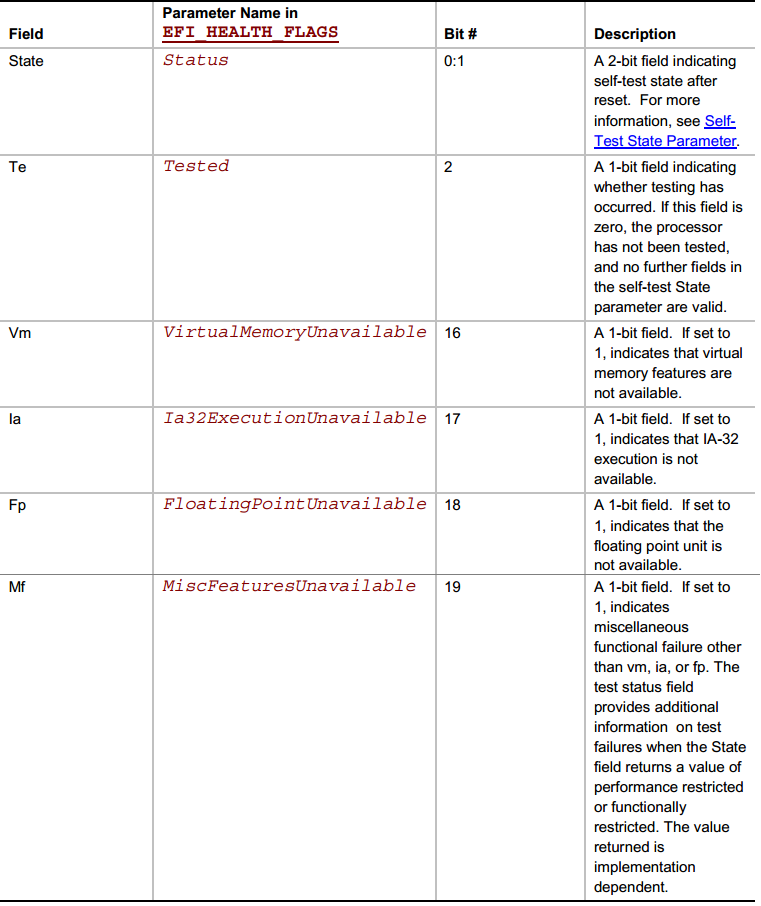

SEC Platform Information PPI 在上面我們有提到SEC利用(強制使用) EFI_PEI_STARTUP_DESCRIPTOR這個資料結構將Handoff德資訊pass給PEI。另外,我們也可以pass"額外"(optional)的PPI EFI_SEC_PLATFORM_INFORMATION_PPI給PEI。這個PPI 抽象化了PEI Fondation所需要用來discover dispatching PEIM的起始位置的platform-specific資訊。這個PPI也可以存在 EFI_PEI_STARTUP_DESCRIPTOR這個資料結構的最後一個參數裡(*DispatchTable)。 Health Flag Bit Format Health Flag Bit Format 在SEC_PLATFORM_INFORMATION_PPI.PlatformInformation() 定義了PFI_HEALTH_FLAGS 存放由microcode、hardware或是Itanium才有的PAL 產生的CPU status。Health Flag的bit format如下圖:

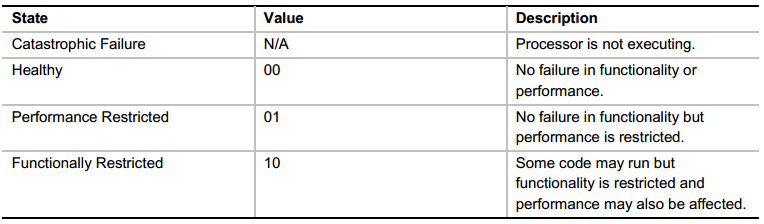

下圖則是每一個bit的說明。 Self-Test State Parameter Self-test state定義的參數for IA-32 Intel® processors 和 Intel® Itanium® processor family 是一樣的。某些 bit可能沒辦法直接對應到IA-32的CPU,這時候讀到的值就會是NULL 下圖說明了每一個bit 的意義。

如果Status顯示functionally restricted,我們可以從vm,ia,fp得到failure的訊息。下面列出導致functionally restricted的情況: 1. Processor 或 PAL偵測到且獨立出錯誤的component,所以不會被使用。 2. Processor必須至少要有一個可以用的memory unit、ALU、shifter及branch unit。 3. Floating-point may be disable。 4. For Itanium,RSE(Register Stack Engine)is not required to work,但register renaming logic必須要能正常work。 5. Processor-controlled caches和register files之間的path在測試的過程中必須要能work。 6. 讀取firmware address space必須要能正常work。 Processor-Specific Detail 下面以IA-32為例,解釋SEC Phase在IA-32架構下的運作狀況。 1. Locating PEI Foundation。 2. 使用 architecture define的Handoff state把control交給PEI。 3. 初始化processor-controlled memory resource例如processor data cache。

參考資料:http://clhjoe.blogspot.tw/2012/05/uefipi-3-securitysec-phase.html VOLUME 1: Platform Initialization Specification Pre-EFI Initialization Core Interface Version 1.2.1 |

||

| ( 知識學習|科學百科 ) |