字體:小 中 大

字體:小 中 大 |

|

|

|

| 2013/07/22 11:54:18瀏覽4528|回應0|推薦2 | |

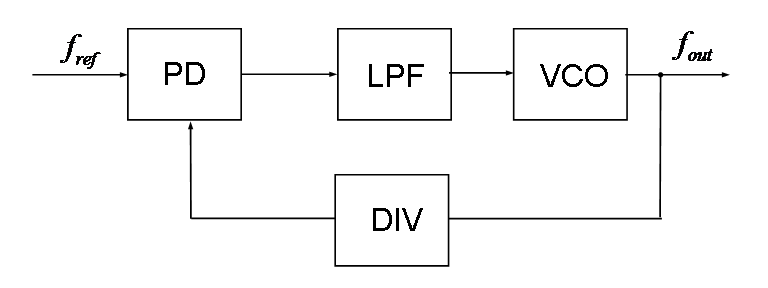

源自<<維基百科>> 鎖相迴路(PLL: Phase-locked loops)是一種利用回授(Feedback)控制原理實現的頻率及相位的同步技術,其作用是將電路輸出的時脈與其外部的參考時脈保持同步。當參考時脈的頻率或相位發生改變時,鎖相迴路會檢測到這種變化,並且通過其內部的回授系統來調節輸出頻率,直到兩者重新同步,這種同步又稱為「鎖相」(Phase-locked)。 - 組成 - 鑒頻鑒相器(PFD)(或鑒相器:PD) 低通濾波器(LPF) 壓控振蕩器(VCO) 回授迴路(通常由一個分頻器(Frequency divider)來實現)

鑒頻鑒相器: 對輸入的參考信號和回授迴路的信號進行頻率和相位的比較,輸出一個代表兩者差異的信號至低通濾波器。 低通濾波器: 將輸入信號中的高頻成分濾除,保留直流部分送至壓控振蕩器。 壓控振蕩器: 輸出一個周期信號,其頻率由輸入電壓所控制。 回授迴路 : 將壓控振蕩器輸出的信號送回至鑒頻鑒相器。通常壓控振蕩器的輸出信號的頻率大於參考信號的頻率,因此需在此加入分頻器以降低頻率。 |

|

| ( 知識學習|科學百科 ) |