字體:小 中 大

字體:小 中 大 |

|

|

|

| 2015/01/31 05:18:56瀏覽98597|回應175|推薦0 | |

|

由於在Google輸入關鍵字「Layout EMC」後,來函向小弟索取完整版者人數有愈多之勢。因此自此時此刻 2020/08/07(五)01:50 起,來函向小弟索取完整版者,請使用銀行帳號轉帳付費新台幣10元整,轉帳之前可先加Line好友確認本人銀行帳號。待Line之系統通知本人帳款入帳後,本人最慢15分鐘內必將【EMC✚EMI】一文,寄給您.....謝謝。 (Line I.D. "paxonjiang"或掃描下方QRcode)

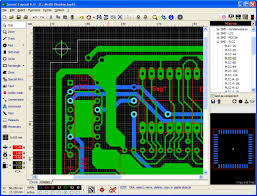

前言 本篇文章為格主本人在Layout業界多年積累之經驗談,只分享給用功進取的您閱讀。另,因UDN部落格網頁預設系統關係,同一篇文章無法同時張貼多張圖片;故,所有貼圖於本文章中皆不顯示。欲所取「完整版(有詳細附圖)」者,請利用上述方式索取。

而EMC又等於EMI+EMS (①、EMI為Electro-Magnatic Interference的省略語,為電磁干擾的意思;②、EMS=Electro Magnatic Susceptibility, 意指:電磁敏感度。) EMC 定義的電磁干擾源,以及後半段的電磁干擾環境,都可以稱之為電磁雜訊,或以NOISE 來稱之。 EMC的組織 概論 在EMI的誕生中,有許多的變數。這是因為EMI是被動元件正常狀態行為以外的結果。如:TRACE在高頻的時候,其等效電路是電感串聯電阻。低頻的時候,其等效電路則是一電感。電阻在高頻的時候,其等效電路是電感串(電阻並聯電容)。低頻的時候,其等效電路就是電阻。電容在高頻的時候, 其等效電路是R,L,C三者串聯。低頻的時候,其等效電路是電容。電感在高頻的時候,其等效電路是L和C並聯。低頻的時候,則是電感。 MICROSTRIP AND STRIPLINE 的差別: 1. MICROSTRIP:指的就是trace 經由一介質連接一完整平面。可提供PCB信號上的壓制,同時也可容許比STRIPLINE要快的CLOCK信號(因為有較小的耦合電容及較低的空載傳輸延遲。其不好的就是PCB外部信號層會幅射能量至外在環境,除非加上金屬屏蔽。 2. STRIPLINE:信號層介於兩個solid plane 。STRIPLINE 可達到較佳的RF 防治,但只能用在較低的速度。因為信號層介於兩個solid plane之間,兩平面會有電容的耦合,導致降低信號的edge rate。 Layout 的基本觀念 二層板:對於二層有二種的layout技術。一種是較老之技術,適用於較低速之元件,一般包含DIP包裝之元件成排或成矩陣撞排列,現在己很少用。 注意以下二點:

四層板:四層板的堆疊只有一種方式。因使用power及ground,EMI的特性 有很大的改善。然而,四層板對產生自電路及trace之RF電流通量 消除之效果並不好。 第一層:Component side,信號及Clock 第二層:Ground Plane 第三層:Power plane 第四層:Solder side,信號及Clocks 如此可得知,當有多於三個完整平面提供的話(即一個power ground) 將最高速clock佈線於相鄰ground plane且不相鄰於power plane,可 得最佳EMI效果。此為在PCB上EMI抑制的基礎觀念。 多層板可提供優良EMC之信號品質,因為經由miocrostrip及stripline 可有效佳之信號阻抗控制。Power及ground plane之分佈阻 抗(distribution inpedance)應儘可能的降低。這一些平面含有來自 於logic crossover之極短暫的突波電流,及信號及匯流排之電容負載。 MICROSTRIP及Stripline應用之主要意義是在於磁通量之互相抵消。 使得傳輸線之電感降低。多數的邏輯族在其pull up/pull down 電流可能極不平均,此使得flux cancellation之效果在信號及ground plane之間比信號及power plane之間要好。因此,使用power plane 作磁通量抵消不能達到最佳的效果,結果會導致信號通量相位偏移增 大電感,差的阻抗控制,及雜訊不穩定。故應使用ground plane要佳。 簡短的重述PCB flux cancellation之重要觀念。 並非有元件的pull up/pull down電流比都是一樣。 舉例來說,有的元件是65mA pull up/65mA pull down,有的則 是65mA pull up/65mA pull down 。此不均狀況造成Ground及 PowerPlane之不平衡。

六層板:有三種方式。先說第一種… 第一種: 這個方式有最佳的EMI 特性,對所以佈線層有較好的Flux cancellation 如下。 第一層:component side, microstrip信號佈線層。 第二層:GROUND PLANE 第三層:Stripline,佈線層,(下跟著填充物質)。 第四層:POWER PLANE 第五層:GROUND PLANE 第六層:solder side, microstrip信號佈線層。

第二種: 為對CLOCK 和高頻元件,較常用的方式 第一層:component side, microstrip信號佈線層 第二層:Ground plane 第三層:Stripline 第四層:Stripline 第五層:Power plane 第六層:solder side microstrip信號佈線層

第三種: 此方式有較佳的EMI特性,因為在Ground及Power平面間有較好 之層間(decoupling )。 第一層:component side, microsrip信號佈線層 第二層:埋入microstrip佈線層 第三層:Ground plane 第四層:Power plane 第五層:埋入microstrip佈線層 第六層:solder side, microstrip佈線層 八層板: 有二種方式,第一種組態,提供較少的磁通量抵消,第二種組態 因有較多的完整平面,提供最大的磁通量抵消。 決定使用第一種或是第二種是基於所須佈線之NET的數量,元件 密度(接腳數),匯流排結構之大小,類比和數位電路,及可用的面積。 第一種: 因在電源及接地平面有較差之通量抵消,此為較差之堆疊方式 有六層佈線層。 第一層:component side, microsrip信號佈線層 第二層:埋入microstrip佈線層 第三層:Ground plane 第四層:Power plane 第五層:Stripline佈線層 第六層:Stripline佈線層 第七層:埋入microstrip佈線層。 第八層:solder side, microstrip佈線層 第二種: 對RF電流有較緊密的磁通量抵消,此方式為較佳之堆疊方式, 其有四層佈線層和四層平面。 第一層:component side, microsrip信號佈線層 第二層:Ground plane 第三層:Stripline佈線層 第四層:Ground plane 第五層:Power plane 第六層:Stripline佈線層 第七層:Ground plane 第八層:solder side, microstrip信號佈線層 十層板: 第一層:component side, microsrip信號佈線層 第二層:Ground plane 第三層:Stripline 佈線層 第四層:Stripline 佈線層 第五層:Ground plane 第六層:Power plane 第七層:Stripline 佈線層 第八層:Stripline 佈線層 第九層:Ground plane 第十層:solder side, microstrip信號佈線層

20-H Rule: 由於磁通的連結,RF電流存在於Power plane之邊。此種層間耦合 稱之(fringing),通常僅見於高速的pcb,當使用高速邏輯及clock時 電源平面間,會互相耦合RF電流且幅射至空中,要減低效應,所有 電源平面要比相鄰的地平面小。 元件的放置 PCB 佈局之前應先注意將元件放置(placement)在適當的位置,一方面需考慮電路板外部接線端子的位置,另一方面也需考慮不同性質的電路應予以適當的區隔。低階類比、高速數位以及雜訊電路(繼電器、高電流開關等等) 應加以分隔以降低子系統間的耦合。當放置元件時,應同時考慮子系統電路間的內部電路繞線,特別是時序及震盪電路。為了去除EMI的潛在問題,應該系統化的檢查元件放置與線路佈局,返覆檢視及修正佈線一直到確定所有的 EMI風險降低到最低為止,簡而言之,事先的防範是將低EMI干擾問題的首要原則。下圖說明將不同性質電路的區隔概念。 數位電路的雜訊與佈線 類比電路的雜訊通常來自於電路板的外部,然而數位電路的雜訊則往往由內部產生,因此如何降低內部雜訊是數位電路板佈線的首要考量因素。 在MCU為主的系統中最敏感的信號是時序、重置和中斷線路,震盪器在開機時尤為敏感。千萬不要將這些線路與高電流開關線路平行,如此易於被電磁交互耦合信號破壞。此效應容易破壞MCU經由中斷碼的執行,引起非預期的重置或中斷。時序信號受到干擾,將造成失相(lose phase)使整個系統失去同步,由於MCU的執行是依據適當的時鐘脈波,因此不要期望它們能在EMI的干擾下恢復正常操作。 震盪器或陶瓷共振時鐘是一種RF電路,必須繞線以減少它的發射位準及敏感性。圖15以一個震盪器或陶瓷共振器與DIP包裝的例子來說明,儘量將震盪電路的配置靠近MCU,若是震盪器或陶瓷共振器的本體很長,就放在PCB之下並將包裝接地。如果震盪器在PCB之外,就將MCU放在離PCB連接器的附近,不然,就將MCU儘量擺近震盪器以縮短繞線距離。震盪線路的地線應該連接元件可能使用最短繞線的接地腳位,電源和接地腳應該直接繞線到PCB的電源部分。圖16 說明PCB 挈b的?/FONT> I/O接地與I/O電纜線的解耦電容佈線方式。 類比電路的雜訊與佈線 低階信號(low-level signal)容易受到數位信號的干擾;如果類比和數位信號必須混雜,要確定彼此的線路相交成90度角,這將會降低交互耦合(cross coupling)的效應。 如果類比電路的signal reference未與數位線路隔離的話,類比-數位轉換器的訊號會受到嚴重的干擾,因此不可將數位電源和接地直接輸入類比-數位轉換器的signal reference線路。這些腳位應直接繞線自母板的電源端之參考電壓,此電壓參考腳位應用 l K歐姆的電阻和l.0 F電容來濾波。

Clock電路 Clock Generator和其相關文件,分佈導線為PCB產生之幅射之重要來源。Clock電路區是定義為包括振器和其buffer,drivers, 及相關元件(包含主元件及被動元件)之實體區域。 而clock電路放在機板的中央位置或是PCB之金屬銅柱接地點,而不要放在邊緣或是靠近I/O的區域。 如果clock要離開板子到附屬卡上,或是排線,或其它週邊等,則將clock電遠離內部連線,直接在連接器處對clock trace作terminated。Clock trace 要成點對點的幅射狀。在連接器端對clock作termonated。可提供一適切之終端,而不會使clock trace因未適當開路變成一單極天線,因而提升信號的品質。 除了對clock trace 有適當的終瑞外,同時也加強對RF的壓制,避免耦合至其它的敏感電路。將振器和晶體直接安裝在PCB板上,不要使用socket。 Socket會增加接腳長度之電感,並使得幅射和耦合路徑增多,造成RF電流及諧波幅射或耦合至內部或外部的環境中。 3W法則 有些訊號,尤其是固定週期的時脈訊號,帶有強烈的高頻成分。當它與其他信號線太靠近時,會將這些已達RF頻率的能量傳到其他的信號上,帶來EMI的困擾。尤其若是被感染的信號線接往I/O的連接頭時,這個問題就更加嚴重。這個問題其實就是前一節所提的隔線干擾。對EMI而言,通常要求信號線中心對信號線中心的距離,維持3倍信號線寬度的距離,稱為3W法則。3W法則可保持70%的電場不互相干擾。若要達到98%的電場不互相干擾,可使用10W的間距。 接地的方式 一個電子設備的設計關鍵即在於具有強韌的與可靠的電源系統,而接地佈局尤為其中關鍵。事實上,接地可視為所有好的PCB設計的基礎。大部分的EMI問題皆可藉由良好的接地來解決。 良好的接地方式是最經濟有效的方式。在PCB的設計上可使用二種接地方式。 但是接地方式的選擇是看產品應用而定。 在應用多點接地,切不可混用單點接地,除非有(isolation)式是依功能區分之子系統。 訊號接地的種類有二 1.單點接地 2.多點接地 單點接地 單點接地又分為串接單點接地和並接單點接地。 從雜訊的觀點來看,串接單點接地是最差的接地方法。 (因為任何導線都會呈現一些電阻,故流經這些導線的電流會使導線產生壓降。)如下圖: 並接單點接地 它在高頻的時候會有一些危險,因為trace在高頻的時候會表現電感的特性,使 得高頻的阻抗升高,而且接地線會產生電感性干擾的問題,如果頻率很高,這一些接地導線可能形成天線將雜訊幅射至外面。所以如果採用單點接地時,接地線 必須可能的縮短,使其高頻的阻抗變低,才不易形成天線。 當元件電路和信號在1MHz以下的時候,單點接地是最好的選擇。 而較高之頻率,power平面和trace的阻抗變的不可忽略。 如果trace 的長度等於或接近信號的四分之一波長,此阻抗會是非常的高。 注意:只要是trace 或ground導體具高阻抗,它就會像天線幅射RF的能量。 所以,在1MHz以上的頻率,一般不使用單點接地。 應用單點接地之信號通常以幅射狀傳遞,產品如:音頻電路,類比儀器, 60Hz和DC power系統。 多點接地 ..... 欲接續觀看此文, 請付款20元購買完整文章, 謝謝。 |

|

| ( 知識學習|隨堂筆記 ) |